Japanese chipmaker Rapidus has developed technology that can reduce the cost of semiconductor production for artificial intelligence applications, seeking to better compete with Taiwan Semiconductor Manufacturing Co. (TSMC) in its preparations for large-scale production, according to “Nikkei Asia.”

Rapidus has created the world’s first prototype interposer cut from a large glass substrate, with the aim of starting mass production in 2028. Interposers serve as platforms for assembling high-bandwidth graphics processing units (GPUs) and memory for artificial intelligence semiconductors, as well as providing interconnections between these components.

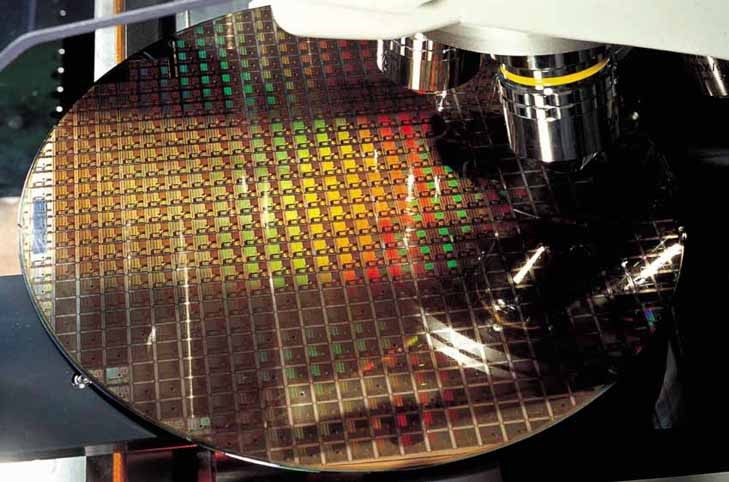

Interposers are typically cut from round silicon wafers measuring 300 millimeters in diameter. This creates waste, because the dividers are generally square.

Rapidus uses a 600mm square glass substrate. The larger size and reduced waste allow ten times more interposers to be produced from a single substrate.

The surface area of the Rapidus prototype is also 30 to 100 percent larger than other interposers, allowing it to accommodate larger chips. The superior electrical performance of glass compared to silicon is also an advantage.

Glass is fragile and susceptible to breakage during processing and shipping, and warping becomes a problem as panels grow. Rapidus hired engineers who had worked at Sharp and other Japanese display makers to address these challenges, and the chipmaker began prototyping in a clean room at its facility in Chitose, northern Japan, in June.

Although a 600 x 600 mm square is large for a semiconductor substrate, it is relatively small compared to panels for liquid crystal displays.

“The adoption of LCD glass processing technology for semiconductors has significantly reduced the barriers,” said Yasumitsu Orii, senior executive director of Rapidus and head of its engineering center.

Competitor TSMC, which makes artificial intelligence semiconductors for Nvidia, uses silicon interposers in its assembly technology. Intel is working towards adopting glass substrates.

“As a late entrant to the market, Rapidus can use the latest materials best suited for artificial intelligence semiconductors without being limited by current practices,” Orii said.

The Japanese company’s plans for mass production of 2-nanometer chips call for starting the wafer circuit manufacturing process in fiscal 2027. Rapidus announced in July that it had produced its first 2-nanometer transistor.

Mass production of the final stage, which involves connecting chips to substrates and packaging them, is expected to begin in 2028. This would enable Japan to have a fully domestic supply chain, from the production of cutting-edge chips to the assembly of artificial intelligence semiconductors.

Japan’s Ministry of Economy, Trade and Industry has pledged 1.72 trillion yen ($11.1 billion) to support Rapidus, of which 180.5 billion yen is earmarked for final-stage processes.

China and Taiwan account for 30% and 28% of global downstream production, respectively, followed closely by Japan with 6%, according to a report from the Boston Consulting Group. These processes were concentrated in areas with low labor costs due to the reliance on human workers, but assembling artificial intelligence chips is more complex. Rapidus is partnering with other Japanese companies to try to automate back-end production.

Rapidus will present its glass substrate prototype at Semicon Japan 2025, which begins this Wednesday in Tokyo.